R7.2a-7(R7.2b-7)

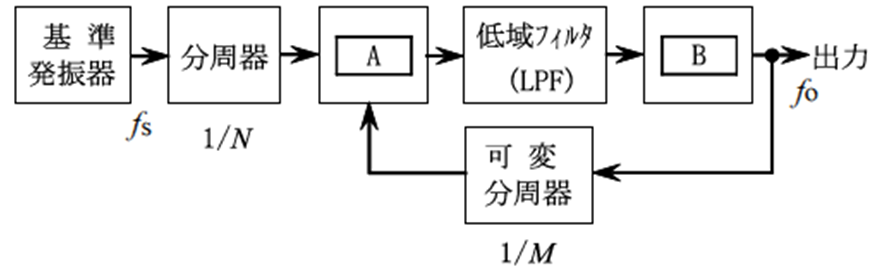

次の記述は、図に示すFM(F3E)送信機の発振部などに用いられるPLL発振回路(PLL周波数シンセサイザ)の原理的な構成例について述べたものである。( )内に入れるべき字句の正しい組合せを下の番号から選べ。なお、同じ記号の( )内には、同じ字句が入るものとする。

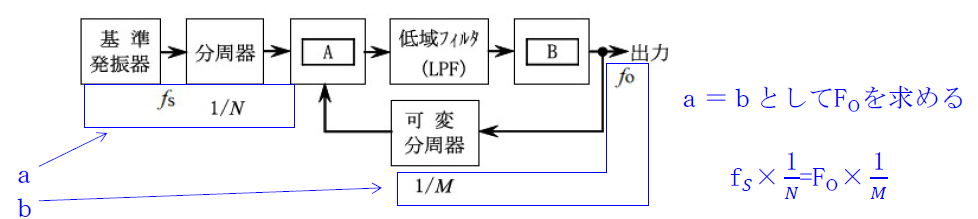

(1) 固定分周器と可変分周器の出力は、( A )に入力される。

(2) 低域フィルタ(LPF)の出力は、( B )に入力される。

(3) 基準発振器の出力の周波数fsを10〔MHz〕、固定分周器の分周比についてNを5、可変分周器の分周比についてMを200としたとき、出力の周波数foは、( C )〔MHz〕になる。なお、PLLはロックしているものとする。

A B C

1 位相比較器 電圧制御発振器(VCO) 400

2 位相比較器 電圧制御発振器(VCO) 200

3 位相比較器 トーン発振器 400

4 平衡変調器 電圧制御発振器(VCO) 400

5 平衡変調器 トーン発振器 200

解答

1 位相比較器 電圧制御発振器(VCO) 400

(1) 固定分周器と可変分周器の出力は、( 位相比較器 )に入力される。

(2) 低域フィルタ(LPF)の出力は、( 電圧制御発振器(VCO) )に入力される。

(3) 基準発振器の出力の周波数fsを10〔MHz〕、固定分周器の分周比についてNを5、可変分周器の分周比についてMを200としたとき、出力の周波数foは、( 400 )〔MHz〕になる。なお、PLLはロックしているものとする。

\(f_s×\frac{1}{N}=f_o×\frac{1}{M}\)

\(f_o=\frac{M}{N}f_s=\frac{200×10M}{5}=400M=400[MHz]\)

コメント